最初の「同期信号を SYNC OUTから取らずに VIDEO INから取る」という方法は、使用する液晶パネル自体に、映像信号から同期分離するための

機能が備わっているものでないと使えない。 ちなみに、私のページでレポートしている液晶パネルでは「CRあっぱれ応援団」「CRヤジキタ」「勝負伝説」

など、追加回路なしで PLAYSTATIONに接続可能なものではこの方法が有効だ。

最後の「74HC14等のロジックICを使って反転回路を組む」という方法は、正極性の同期信号(=INV側に接続)が必要な場合にも

有効だ。 とりあえず簡単に作れるレベルなので、早速製作例をどうぞ。

|

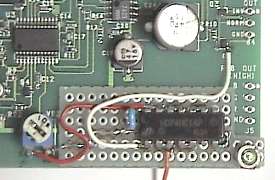

さて、右の写真はすでに RGBコンバータ V2に 74HC14による同期反転回路を組み込んだ状態のものだ。 ユニバーサル基板の切れ端を削り、

表裏を逆に使って銅箔面に回路を組み、そのままネジ穴に共締めしてある。 基板の余分なスペースがこういうところで役に立つのが皮肉なところだ (^^;

用意するものは、74HC14(足を短く切っておく)と積層セラミック 0.1μF、それにユニバーサル基板および配線材の切れ端があれば OKだ。 大した回路ではないが

信号の引き出しポイントについて少し補足しておくと、

- ・電源

- CONTRAST(VR2)の左側端子

※4Vで動作させている

・GND

- CONTRAST(VR2)の右側端子

※スズメッキ線を基板にはわせて固定も兼ねる

・同期信号引き出し

- Q2のB =右下端子(J4にパターンが伸びていない方)

回路図は二通りの図を用意したので、見やすい方をどうぞ。

尚、ICの空きユニット処理の都合で 2-3、4-5、14-13、12-11、10-9のピン間にハンダを盛ってつないだ上、1Pinに

引き出した同期信号(白線)を供給している。 この状態で、2-3Pinから NORM、4-5Pinから INV側同期信号が取り出せる。

|

|

|

|

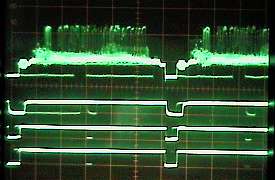

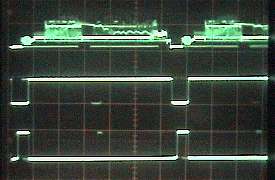

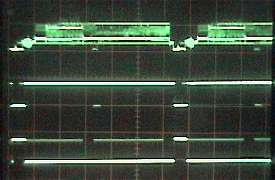

結果はごらんの通り、INV側も遅れはかなり改善されているのが読み取れる筈だ。

|

|